智原推DDR/LPDDR IP 整合聯電22ULP與14FFC製程

鉅亨網記者魏志豪 台北

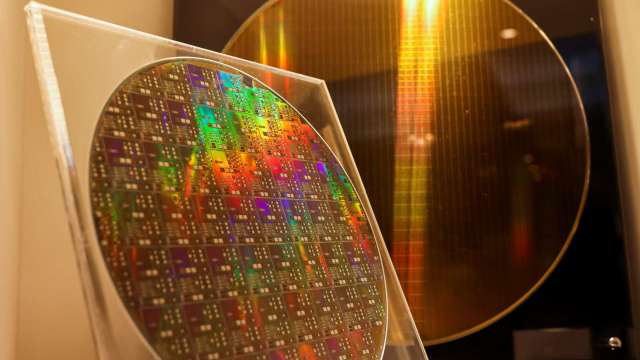

ASIC 與 IP 業者智原 (3035-TW) 今 (22) 日宣布,推出支援第三至第五代 DDR/LPDDR 的通用實體層 IP,適用於聯電(2303-TW)(UMC-US) 22ULP 與 14FFC FinFET 製程。智原持續致力於提供優化的自有 IP 解決方案,協助 ASIC 客戶提升開發效率與產品成本競爭力與降低風險。

智原營運長林世欽表示,隨著 SoC 設計日益複雜,市場對高效能與低功耗的記憶體解決方案需求不斷提升,公司提供涵蓋控制電路、實體層及子系統整合服務的完整 DDR/LPDDR IP 解決方案,協助客戶加速設計時程、降低開發風險,並以高品質且可靠的記憶體子系統,滿足先進應用的設計需求。

智原的 DDR/LPDDR 實體層 IP 解決方案,已廣泛應用於多項 SoC 設計案中,經過矽驗證及單晶片系統整合驗證,其高度穩定性與相容性完全符合 JEDEC 規範,可確保與記憶體晶片間資傳輸效能,並優化功耗表現。

智原 22ULP PHY 支援低至 0.8V 的操作電壓,特別適用於行動裝置、5G 與物聯網等功耗敏感的應用;而 14 奈米 PHY 支援 DDR5/LPDDR5,提供高達 6400Mbps 的傳輸速率,並內建參數調整機制、阻抗匹配校正與 DFE 等功能,確保訊號傳輸的品質與穩定性。

- 主動選股績效夯!專家配置一鍵打包

- 掌握全球財經資訊點我下載APP

鉅亨贏指標

了解更多- 講座

- 公告

上一篇

下一篇